問題

キャッシュメモリに関する記述のうち,適切なものはどれか。

- ア:キャッシュメモリにヒットしない場合に割込みが生じ,プログラムによって主記憶からキャッシュメモリにデータが転送される。

- イ:キャッシュメモリは,実記憶と仮想記憶とのメモリ容量の差を埋めるために採用される。

- ウ:データ書込み命令を実行したときに,キャッシュメモリと主記憶の両方を書き換える方式と,キャッシュメモリだけを書き換えておき,主記憶の書換えはキャッシュメモリから当該データが追い出されるときに行う方式とがある。

- エ:半導体メモリのアクセス速度の向上が著しいので,キャッシュメモリの必要性は減っている。

基本情報技術者平成30年春期 午前問11

CPUの性能を向上させるために使用するメモリであるキャッシュメモリ。基本情報技術者試験や応用情報技術者試験では、このキャッシュメモリの動作に関する問題が出題されます。

本記事では、キャッシュメモリの仕組みについて図解で分かりやすく解説していきます。

本記事で学べること

- キャッシュメモリの役割を理解する

- ダイレクトマップ方式、フルアソシアティブ方式、セットアソシアティブ方式の動きを理解する

- ライトスルー方式とライトバック方式の動きを理解する

- ヒット率の計算方法を覚える

- 基本情報技術者試験の過去問の解き方を学ぶ

目次

キャッシュメモリとは

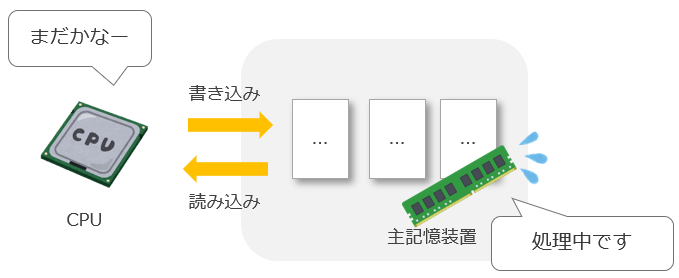

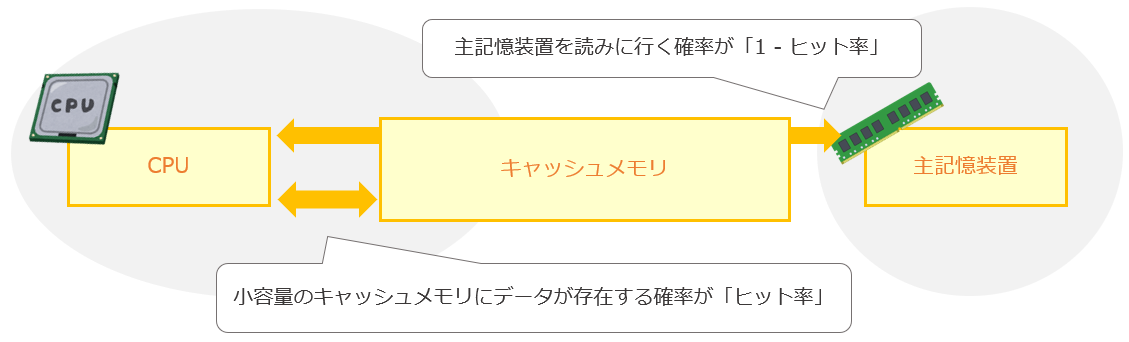

キャッシュメモリとは、CPUと主記憶装置(メインメモリ)の間にある記憶装置のことです。

コンピュータの頭脳であるCPUは、コンピュータの動作に必要なデータや命令を主記憶装置とやり取りしながら処理します。しかし、高速で動作するCPUに比べると主記憶装置の処理は遅く待ち時間が発生してしまいます。

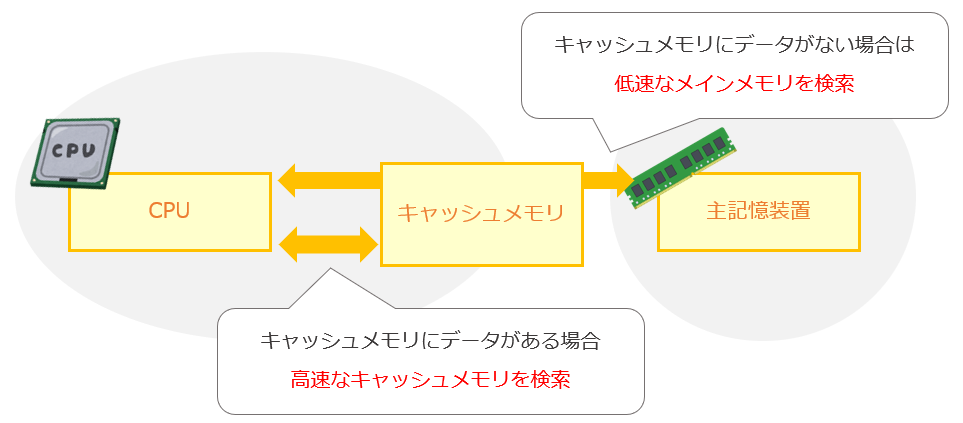

そこで使用するのがキャッシュメモリです。キャッシュメモリは主記憶装置よりも高速に動作するため、CPUがメモリにアクセスする時間を短縮できCPU性能の向上に繋がります。

CPUはキャッシュメモリにデータが存在する場合は、高速なキャッシュメモリからデータを読み出し、キャッシュメモリにない場合は低速な主記憶装置からデータを読み出します。

主記憶装置からデータを読み出すときは、主記憶装置のデータをキャッシュメモリにも保存しておきます。

主記憶装置のデータをキャッシュメモリのどの位置(ロケーション)に格納するかを決定する方式には「ダイレクトマップ方式」「フルアソシアティブ方式」「セットアソシアティブ方式」があります。

スポンサーリンク

キャッシュメモリへの格納

キャッシュメモリはデータをブロックという単位で管理しています。そのため、主記憶装置にあるデータはブロックという一定長の単位ごとにキャッシュメモリに格納します。

主記憶装置のデータをキャッシュメモリのどの位置(ロケーション)に格納するかを決める方式には次の3種類があります。

ダイレクトマップ方式

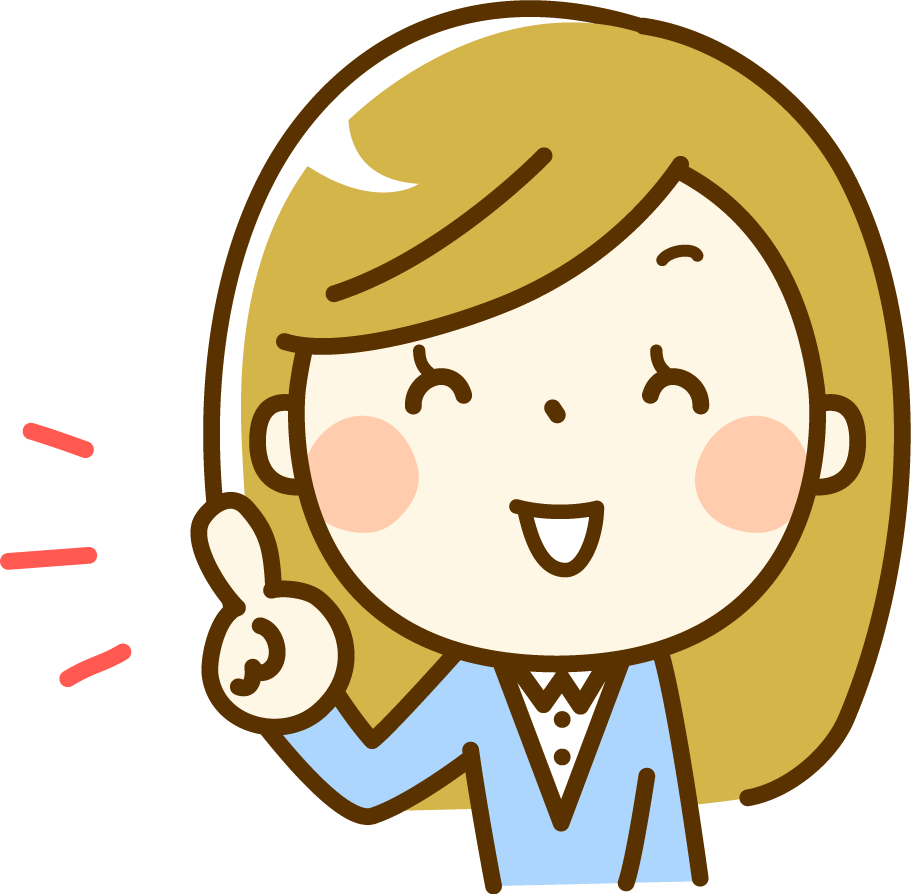

ダイレクトマップ方式とは、主記憶装置のブロック番号に一定の計算を行うことでキャッシュメモリの格納位置を算出する方式のことです。

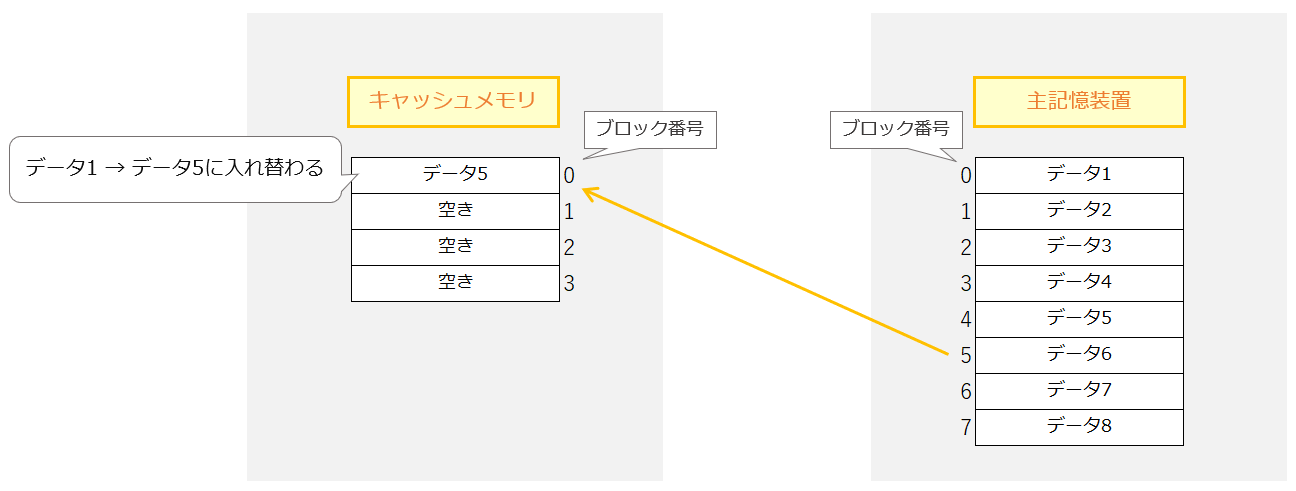

一定の計算式でキャッシュメモリのどの位置(ロケーション)に格納するか決めるため、キャッシュメモリに空きの領域が残っていたとしても、空きのある部分ではなく計算結果の位置にデータを格納します。

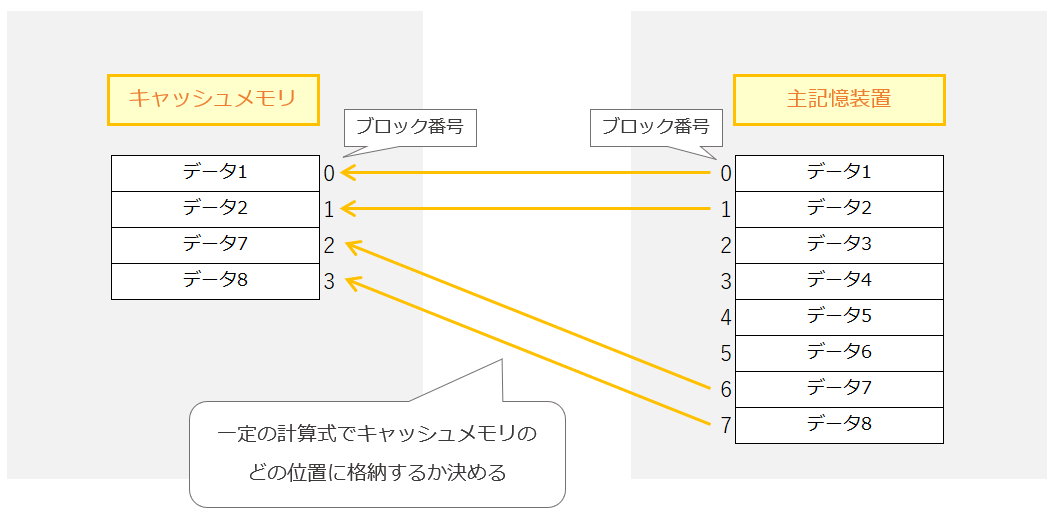

次図のようにキャッシュメモリのブロック1~3が空きの状態でも

一定の計算式で求めた結果がブロック0であれば、キャッシュメモリのブロック0のデータを入れ替えます。

フルアソシアティブ方式

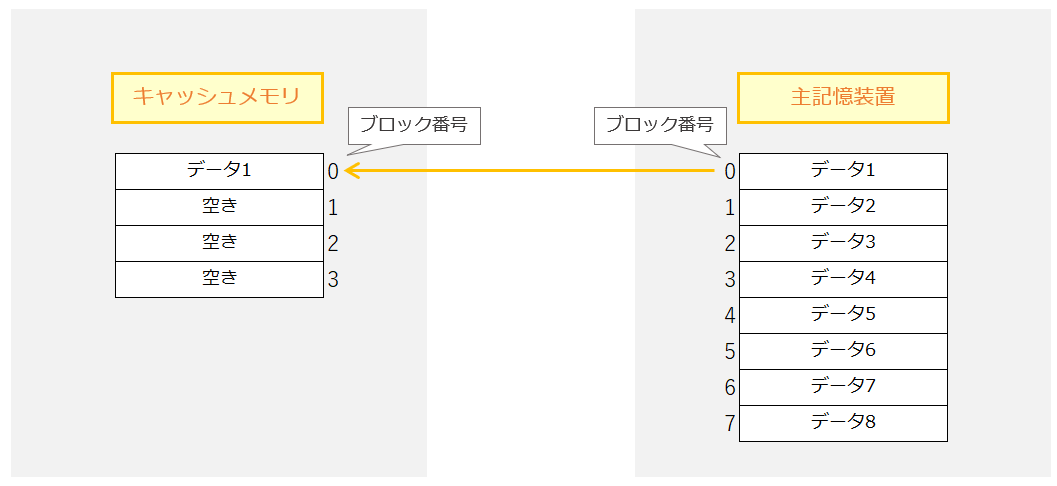

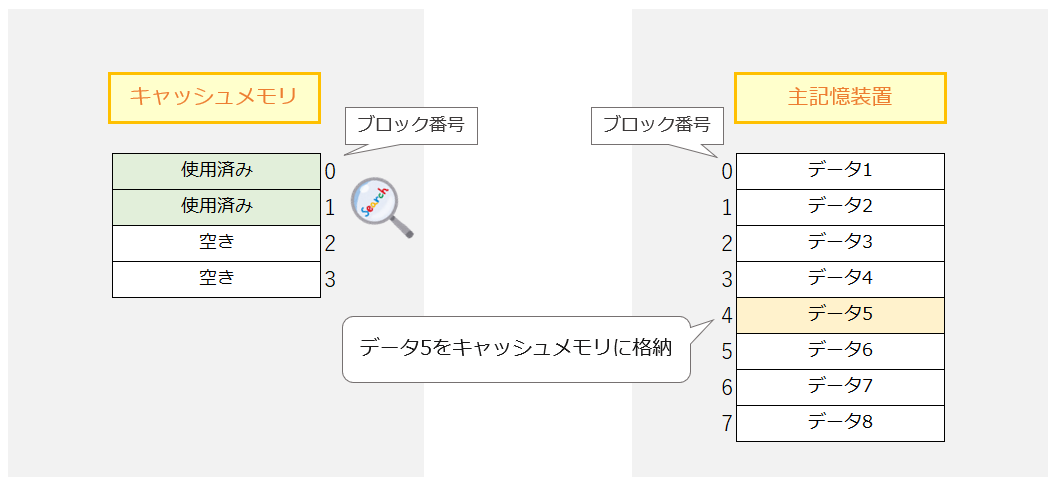

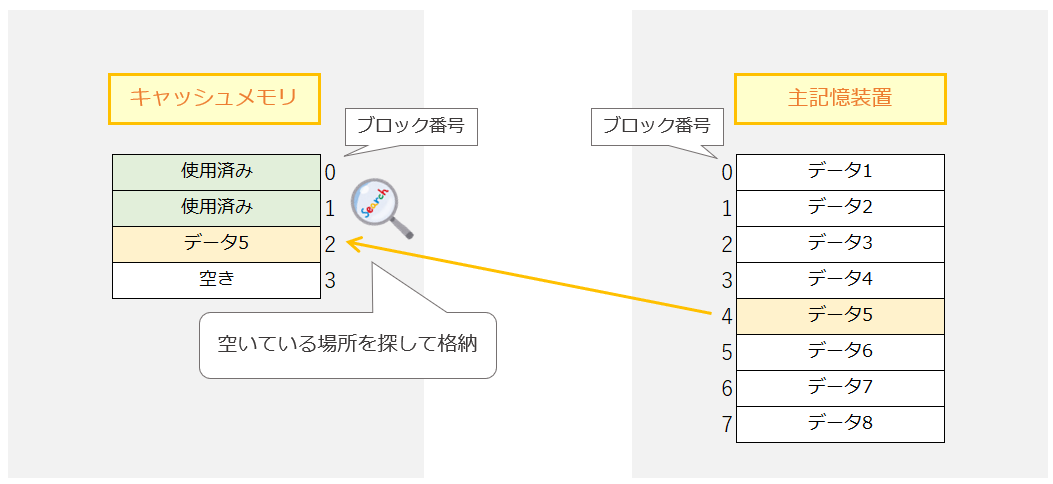

フルアソシアティブ方式とは、主記憶装置のデータをキャッシュメモリ内の空き領域に保管する方式のことです。

次図のようにキャッシュメモリのブロック2とブロック3が空きの状態で、主記憶装置のデータ5をキャッシュメモリにフルアソシアティブ方式で格納すると

キャッシュメモリ内の空き領域を探し出し、その位置に主記憶装置のデータを格納します。

フルアソシアティブ方式は、キャッシュメモリの空いている場所にデータを保管するので効率よくデータを格納できるが、空いている場所を探すための検索コストが大きく速度的に難があります。

セットアソシアティブ方式

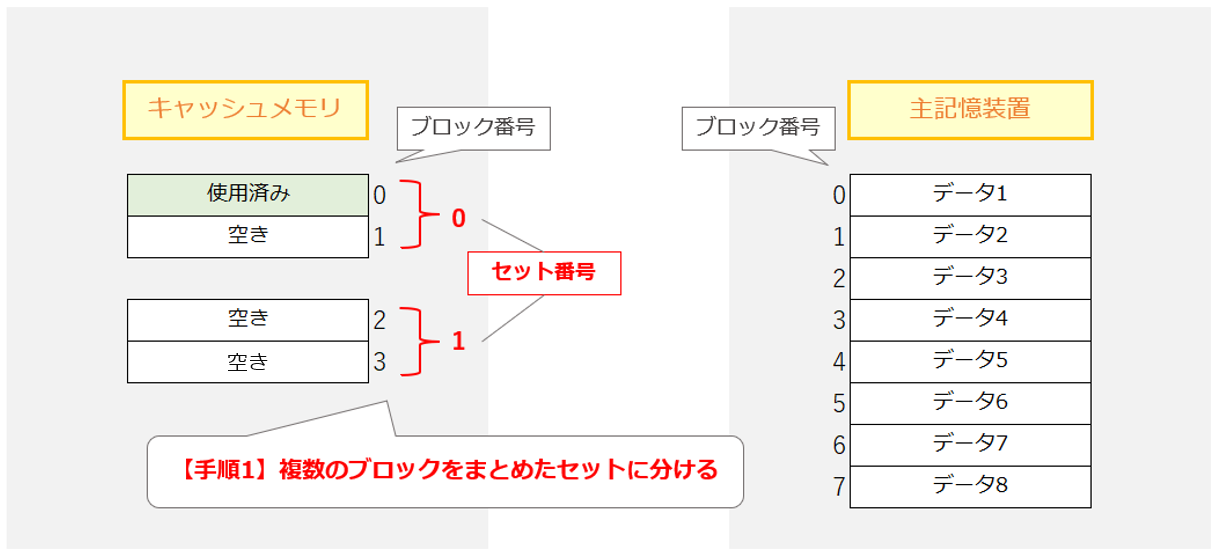

セットアソシアティブ方式は、ダイレクトマップ方式とフルアソシアティブ方式の中間的な性質を持つ方式で、次の手順でキャッシュメモリのどの位置(ロケーション)に格納するか決めます。

スポンサーリンク

【手順1】キャッシュメモリのブロックをセットに分ける

セットアソシアティブ方式では、キャッシュメモリのブロックをセットに分けます。(セットとは2つ以上のブロックを一つにまとめたもの)

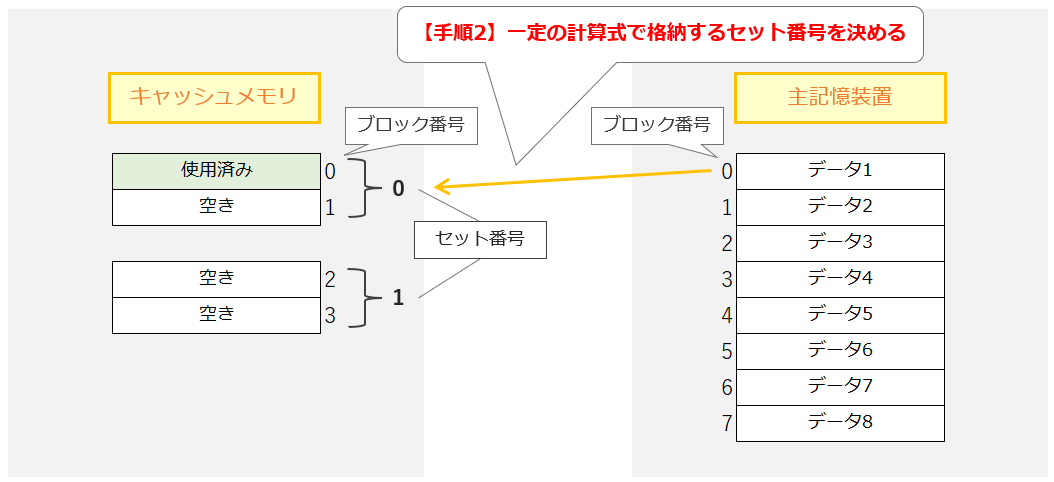

【手順2】一定の計算式で格納するセット番号を決める

キャッシュメモリのブロックをセットに分けたら、主記憶装置のデータをどのセットに格納するか一定の計算式で求めます。

【手順3】セット内の空いている場所に格納

主記憶装置のデータを格納するセット番号を求めたら、セット内のいずれかの場所にデータを格納します。(セット内に空き領域がないかを探し、空きがあれば空いている場所にデータを格納する)

キャッシュメモリへの書き込み

キャッシュメモリは読み出しだけではなく書き込みにも使用します。ただキャッシュメモリに書き込んだ内容はどこかのタイミングで主記憶装置にも反映させる必要があります。

このキャッシュメモリに書き込んだ内容を主記憶装置へ反映させるための方式には次の2種類があります。

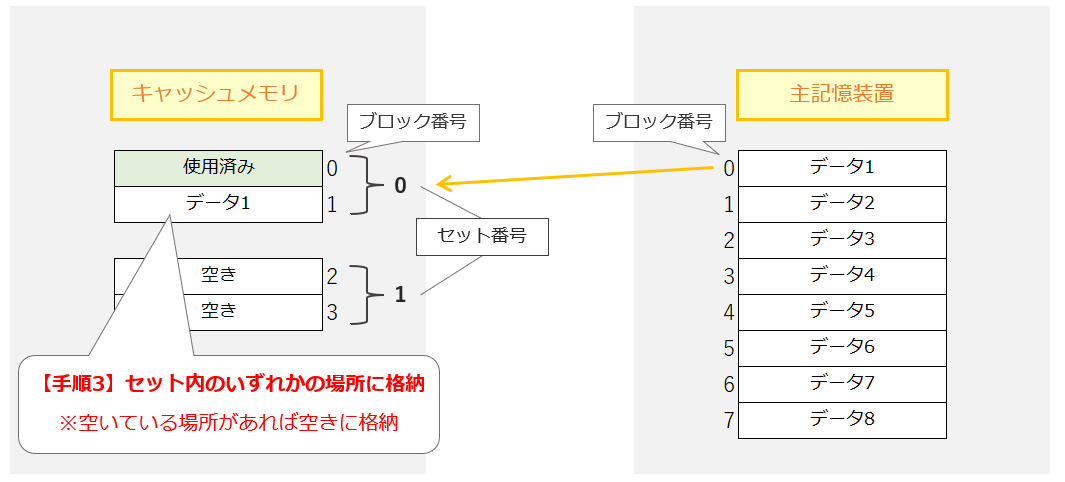

ライトスルー方式

ライトスルー方式とは、CPUがキャッシュメモリに書き込みを行う際、同時に主記憶装置へも書き込みを行う方式のことです。

ライトスルー方式では、高速なキャッシュメモリと低速な主記憶装置の両方に書き込みを行います。そのため、読み出し時はキャッシュメモリによって高速に動作するが、書き込み時の性能はまったく向上しません。

ただし、キャッシュメモリと主記憶装置のデータは常に一致しているため一貫性を保つことができます。

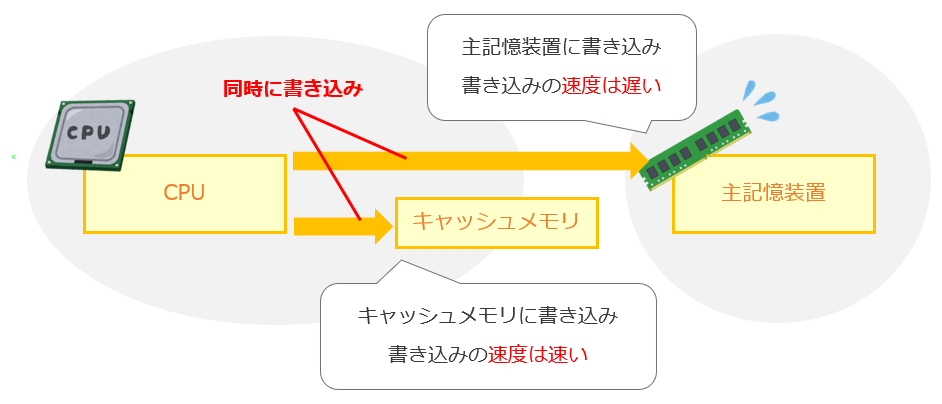

ライトバック方式

ライトバック方式とは、CPUがキャッシュメモリに書き込みを行う際、普段はキャッシュメモリにしか書き込みを行わず、主記憶装置への書き込みは後で行う方式のことです。

ライトバック方式では、普段はキャッシュメモリにだけ書き込みを行います。

そして、キャッシュメモリからデータが追い出されるタイミング(キャッシュメモリは小容量のため、データが入らなくなると古い内容は新しい内容で上書きされる)で主記憶装置に書き込みを行います。

ライトバック方式では、普段は高速なキャッシュメモリにしか書き込みを行わないため、読み出し時だけではなく書き込み時の性能も向上します。

ただし、キャッシュメモリと主記憶装置のデータが必ずしも一致しているとは限らず、ライトスルー方式に比べ制御が難しいという短所があります。

キャッシュメモリにデータが存在する確率

キャッシュメモリは主記憶装置より容量が小さいです。そのため目的とするデータが必ずキャッシュメモリに入っているとは限りません。

キャッシュメモリに目的のデータが存在する確率のことを「ヒット率」といいます。

また、キャッシュメモリに存在しない確率(主記憶装置を読みに行く確率)は「1-ヒット率」で求めることができます。

スポンサーリンク

実効アクセス時間の求め方

実効アクセス時間とは、キャッシュメモリを使ったコンピュータの平均的なアクセス時間のことです。

実効アクセス時間は次の式で求めることができます。

実効アクセス時間の求め方

キャッシュのアクセス時間 × ヒット率 + 主記憶装置のアクセス時間 × (1 - ヒット率)

基本情報技術者試験 過去問の解説

基本情報技術者平成30年春期 午前問11

問題

キャッシュメモリに関する記述のうち,適切なものはどれか。

- ア:キャッシュメモリにヒットしない場合に割込みが生じ,プログラムによって主記憶からキャッシュメモリにデータが転送される。

- イ:キャッシュメモリは,実記憶と仮想記憶とのメモリ容量の差を埋めるために採用される。

- ウ:データ書込み命令を実行したときに,キャッシュメモリと主記憶の両方を書き換える方式と,キャッシュメモリだけを書き換えておき,主記憶の書換えはキャッシュメモリから当該データが追い出されるときに行う方式とがある。

- エ:半導体メモリのアクセス速度の向上が著しいので,キャッシュメモリの必要性は減っている。

基本情報技術者平成30年春期 午前問11

キャッシュメモリに関する記述のうち、適切なものはどれか解答のア~エを順番に確認していきます。

解答ア

■キャッシュメモリにヒットしない場合に割込みが生じ,プログラムによって主記憶からキャッシュメモリにデータが転送される。

不正解:キャッシュメモリに存在しない場合は、主記憶からデータを読み出します。このとき割込みは発生しません。

解答イ

■キャッシュメモリは,実記憶と仮想記憶とのメモリ容量の差を埋めるために採用される。

不正解:キャッシュメモリは、主記憶とCPUの速度差を埋めるものです。

解答ウ

■データ書込み命令を実行したときに,キャッシュメモリと主記憶の両方を書き換える方式と,キャッシュメモリだけを書き換えておき,主記憶の書換えはキャッシュメモリから当該データが追い出されるときに行う方式とがある。

正解:キャッシュメモリと主記憶の両方を書き換える方式がライトスルー方式。キャッシュメモリだけを書き換えておき、主記憶の書換えはキャッシュメモリから当該データが追い出されるときに行う方式がライトバック方式です。

解答エ

■半導体メモリのアクセス速度の向上が著しいので,キャッシュメモリの必要性は減っている。

不正解:メモリのアクセス速度は向上しているが、CPUの処理速度も向上しているためキャッシュメモリの必要性は増している。

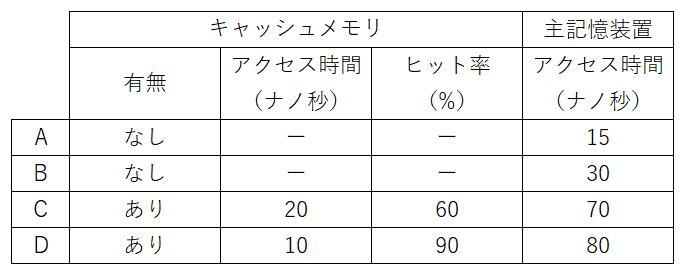

基本情報技術者平成31年春期 午前問10

実効アクセス時間は次の式で求めることができます。

キャッシュのアクセス時間 × ヒット率 + 主記憶装置のアクセス時間 × (1 - ヒット率)

AとBはキャッシュメモリがなく計算の必要がないため、CとDの実効アクセス時間を求めます。

実効アクセス時間の計算

【Aは計算不要】15[ナノ秒]

【Bは計算不要】30[ナノ秒]

【Cの計算】

20[ナノ秒] × 0.6 + 70[ナノ秒] × (1 - 0.6)

= 12[ナノ秒] + 28[ナノ秒]

= 40[ナノ秒]

【Dの計算】

10[ナノ秒] × 0.9 + 80[ナノ秒] × (1 - 0.9)

= 9[ナノ秒] + 8[ナノ秒]

= 17[ナノ秒]

基本情報技術者試験おすすめの参考書・問題集

| いちばんやさしい 基本情報技術者 | 『基本情報技術者試験』試験に、短期間で一発合格するための試験対策本。ITの知識がまったくない、未経験者やでもスラスラと学習を進められるよう、丁寧に解説。 |

| かやのき先生の基本情報技術者教室 | 基本情報技術者をめざす方のためのやさしいオールインワンタイプの参考書&問題集。イラストや豊富な図解・例え話を駆使して理解しやすく・記憶に残りやすいように説明。 |

| 基本情報技術者 パーフェクトラーニング過去問題集 | 科目A・Bともに万全の対策ができる、定番の過去問題集!科目A・科目Bの両方について万全の対策ができる。 |

| キタミ式イラストIT塾 基本情報技術者 | すべての解説をイラストベースで行っているため,とてもわかりやすい解説本。いちばん最初に読む基本情報技術者試験関連の書籍を探している人におすすめ! |

| 出るとこだけ!基本情報技術者[科目B] | 基本情報技術者【科目B】対策の定番書!前提知識+解き方+試験問題を掲載。効率よく学習できる。 |

| 基本情報技術者 合格教本 | 出題範囲を体系的にきちんと理解しながら学習したい人におすすめ!基本情報技術者試験の定番テキストの改訂版。 |

| 基本情報技術者 超効率の教科書+よく出る問題集 | 動画でスムーズに学習スタート、テキストでしっかり理解度を深める!よく出る問題を反復学習することで、合格に直結するチカラが身に付く! |