メモリインターリーブ

メモリインターリーブ(英:memory interleaving)とは、主記憶装置(メインメモリ)へのアクセスを高速化する手法のひとつです。

CPUはコンピュータの動作に必要なデータや命令を主記憶装置とやり取りしながら処理します。しかし、高速に動作するCPUに比べると主記憶装置の処理は遅く待ち時間が発生してしまいます。

この主記憶装置へのアクセスを高速化するための手法がメモリインターリーブです。

メモリインターリーブの必要性

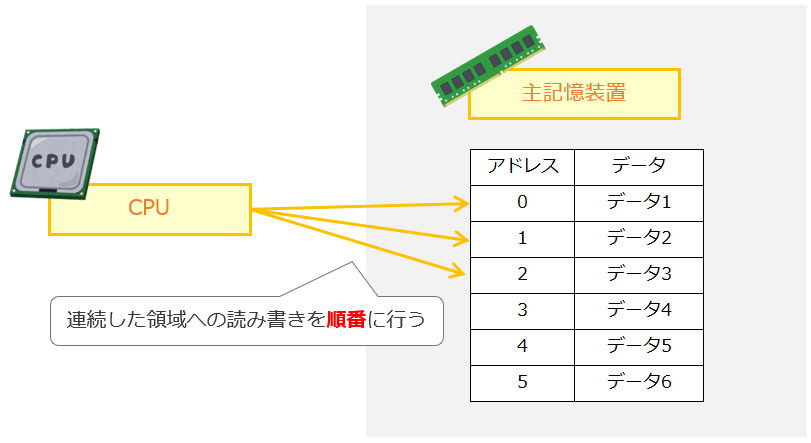

CPUが主記憶装置へアクセスするとき、連続した領域へ順番にアクセスすることがよくあります。

次の図例のように、CPUは「メモリアドレス0のデータを読み込み」次に「メモリアドレス1のデータを読み込み」次に「メモリアドレス2のデータを読み込み」と連続した領域のデータに対して順番にアクセスします。

このとき、高速に動作するCPUに比べると主記憶装置の処理は遅いため、連続した領域へ順番にアクセスするも毎回待ち時間が発生してしまいます。

この問題を解消するための手法のひとつが「メモリインターリーブ」です。

メモリインターリーブの仕組み

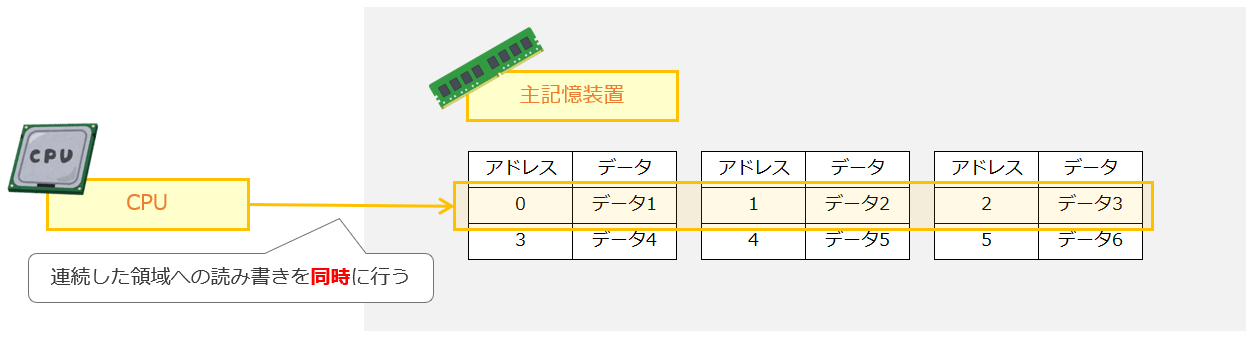

メモリインタリーブでは、主記憶装置内を複数の区画(バンク)に分割します。

複数のバンクにまたがって連続したアドレスを割り当てることで、連続した領域へのアクセスを同時に行うことができます。

以下はメモリインタリーブのイメージ図です。

主記憶装置内を複数の区画(バンク)に分割し、複数のバンクにまたがって連続したアドレスを割り当てています。その結果「メモリアドレス0」~「メモリアドレス2」のデータを一気に読み出す(もしくは書き込み)ことができます。

1回のアクセスで複数のデータを取得できるため、その分 高速に動作します。

ただしメモリインタリーブは、連続した領域へのアクセス以外(ランダムアクセスや連続しないデータへのアクセス)あまり効果は期待できません。

まとめ

メモリインターリーブとは

- 主記憶装置へのアクセスを高速化するための手法のひとつ

- 主記憶装置内を複数のバンクに分割することで、連続した領域への同時アクセスを可能にしている

helpful

この記事は役に立ちましたか?